## DESCRIPTION

The MT6832 is a 3W, filterless, ultra-low EMI noise, single-ended input, stereo class-D audio amplifier. It is low noise, filter-free with PWM architecture, minimizing external component count, PCB area, system cost.

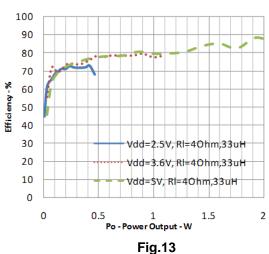

The chip features very low 0.1% THD+N, high 90dB SNR, and therefore offer high quality sound. MT6832 delivers up to 3W per channel into a  $4\Omega$  load with an efficiency up to 90%.

The MT6832 features a low-power consumption shutdown mode. The gain of the MT6832 is externally configurable which allows independent gain control from multiple sources by summing the signals. Output short circuit and thermal overload protection prevent the device from damage during fault conditions

The high efficiency and a low shutdown current make the MT6832 an ideal choice for both battery-powered speakers and portable devices.

MT6832 integrates Maxic's unique EMI suppression technique, can work with FM tuner without extra Ferrite-bead components.

# **ORDERING INFORMATION**

| Part #   | Package | Remarks    |

|----------|---------|------------|

| MT6832   | SOP-16  | Tube       |

| 10110032 | 30F-10  | 50pcs/tube |

### FEATURES

- 3W output at 10% THD with a 4Ω load and 5V power supply

- 2.5V~5.5V single supply operation

- Filterless and ultra-low EMI, can work with FM tuner without extra Ferrite-bead components

- Less than 0.1% THD+N

- Excellent Power up/down "Pop sound" suppression

- Low quiescent current and low-power shutdown current

- Few external components to save the space and cost

- Over current/Short circuit and over temperature protection

- Available in SOP16 package (Pb-free)

## APPLICATION

- Mobile phone

- Portable audio product

- Portable media player

- Personal navigation device

- Video game

- Cordless phone

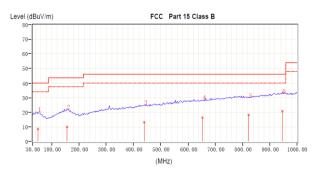

## **RADIATED EMISSION**

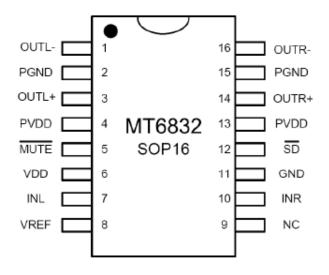

# **PIN CONFIGURATIONS**

# **PIN DESCRIPTIONS**

| Pin# | Symbol | Function                                       |  |

|------|--------|------------------------------------------------|--|

| 1    | OUTL-  | Left channel negative output                   |  |

| 2    | PGNDL  | Left channel ground                            |  |

| 3    | OUTL+  | Left channel positive output                   |  |

| 4    | PVDDL  | Left channel power supply                      |  |

| 5    | MUTE   | Mute control input(active low); Internal has a |  |

|      |        | 300kohm resistor pull to VDD.                  |  |

| 6    | VDD    | Analog power supply                            |  |

| 7    | INL    | Left channel audio input                       |  |

| 8    | VREF   | Internal Analog reference. Connect a 0.1uF     |  |

|      |        | capacitor to GND.                              |  |

| 9    | NC     | No Connection                                  |  |

| 10   | INR    | Right channel audio input                      |  |

| 11   | GND    | Analog ground                                  |  |

| 12   | SD     | Shutdown pin(active low) ; Internal has a      |  |

|      | 30     | 300kohm resistor pull to VDD.                  |  |

| 13   | PVDDR  | Right channel power supply                     |  |

| 14   | OUTR+  | Right channel positive output                  |  |

| 15   | PGNDR  | Right channel ground                           |  |

| 16   | OUTR-  | Right channel negative output                  |  |

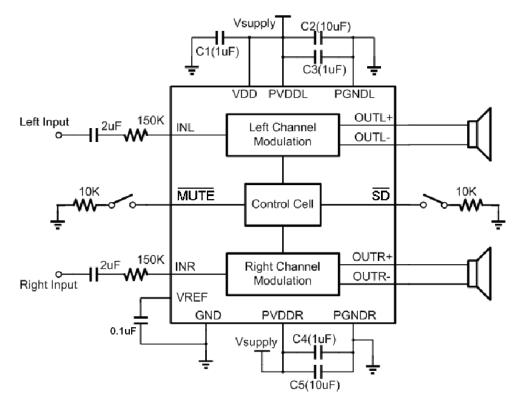

# **TYPICAL APPLICATION CIRCUITS**

MT6832: Single-Ended Input Application Circuit

Note: C1~C5 are ceramic capacitor and should be put as close to MT6832 as possible!

# **ABSOLUTE MAXMUM RATINGS**

|      |                                           | In active mode          | –0.3 V to 6 V                |  |  |

|------|-------------------------------------------|-------------------------|------------------------------|--|--|

| VDD  | Supply voltage                            | In $\overline{SD}$ mode | –0.3 V to 7 V                |  |  |

| VI   | Input voltage                             |                         | –0.3 V to VDD + 0.3 V        |  |  |

|      | Continuous total power dissipation        |                         | See Dissipation Rating Table |  |  |

| TJ   | Operating junction                        | n temperature           | –40°C to 150°C               |  |  |

| Tstg | Storage temperat                          | ure                     | –65°C to 150°C               |  |  |

|      | Lead temperature from case for 10 seconds |                         | 260°C                        |  |  |

# THERMAL CHARACTERISTIC

| Symbol | Description                | Value | Units |

|--------|----------------------------|-------|-------|

| θJA    | Maximum Thermal Resistance | 80    | °C/W  |

# **RECOMMENTED OPERATING CONDITIONS**

|     |                                 |                   | MIN | MAX     | UNIT |

|-----|---------------------------------|-------------------|-----|---------|------|

| VDD | Supply voltage                  |                   | 2.5 | 5.5     | V    |

| VIH | High-level input voltage        | <u>SD</u>         | 1.3 | VDD     | V    |

| VIL | Low-level input voltage         | <u>SD</u>         | 0   | 0.35    | V    |

| VIC | Common mode input voltage range | VDD = 2.5V - 5.5V | 0.5 | VDD-0.8 | V    |

| TA  | Operating free-air temperature  |                   | -40 | 85      | °C   |

# **ELECTRICAL CHARACTERISTICS**

|                       | PARAMETER                                | TEST CONDITIONS                   | MIN | TYP                     | MAX | UNIT |  |

|-----------------------|------------------------------------------|-----------------------------------|-----|-------------------------|-----|------|--|

| VOS                   | Output offset voltage                    | Inputs AC grounded,               |     | 2                       | 19  | mV   |  |

|                       |                                          | VDD = 2.5 V to 5.5 V              |     |                         |     |      |  |

| IIH                   | High-level input current                 | VDD = 5.0 V, VI = 5.3 V           |     |                         | 50  | μA   |  |

| IIL                   | Low-level input current                  | VDD = 5.0 V, VI = -0.3 V          |     |                         | 5   | μA   |  |

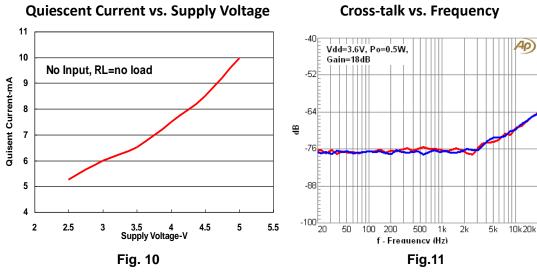

|                       |                                          | VDD = 5.0 V, no load              |     | 10                      |     |      |  |

| I(Q)                  | Quiescent current                        | VDD = 3.6 V, no load              |     | 6.5                     |     | mA   |  |

|                       |                                          | VDD = 2.5 V, no load              |     | 5.3                     |     |      |  |

| I(SD)                 | Shutdown current                         | $V(\overline{SD}) = 0.35 V,$      |     | 10                      |     | μΑ   |  |

|                       |                                          | VDD = 3.6 V                       |     |                         |     |      |  |

|                       | Otatia duain accurac                     | VDD = 2.5 V                       |     | 715                     |     |      |  |

|                       | Static drain-source                      | VDD = 3.6 V                       |     | 540                     |     | mΩ   |  |

| r <sub>DSON</sub> (P) | on-state resistance                      | VDD = 5.0 V                       |     | 490                     |     |      |  |

|                       |                                          | VDD = 2.5 V                       |     | 720                     |     |      |  |

| · (NI)                | Static drain-source                      | VDD = 3.6 V                       |     | 550                     |     | mΩ   |  |

| r <sub>DSON</sub> (N) | on-state resistance                      | VDD = 5.0 V                       |     | 510                     |     |      |  |

|                       | Output impedance in SHUTDOWN mode        | $\vee(\overline{SD}) = 0.35 \vee$ |     | >1                      |     | kΩ   |  |

| f(sw)                 | Switching frequency                      | VDD = 2.5 V to 5.5 V              |     | 300                     |     | kHz  |  |

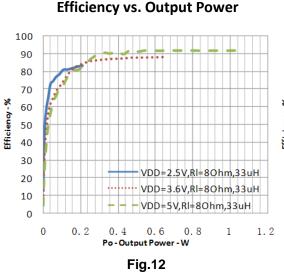

| A <sub>GAIN</sub>     | Amplifier Gain VDD = 2.5 V to 5.5 V      |                                   |     | $\frac{600k\Omega}{Ri}$ |     | V/V  |  |

| $R_{UP_{SD}}$         | Resistance from $\overline{SD}$ to VDD   |                                   |     | 300/1000                |     | kΩ   |  |

| R <sub>UP_MUTE</sub>  | Resistance from $\overline{MUTE}$ to VDD |                                   |     | 300/1000                |     | kΩ   |  |

#### TA = $25^{\circ}$ (unless otherwise noted)

# **OPERATING CHARACTERISTICS**

### TA = 25 $^{\circ}$ C (unless otherwise noted)

|       | PARAMETER       | TEST CONDITIONS                            |                      | MIN | TYP   | MAX | UNIT |

|-------|-----------------|--------------------------------------------|----------------------|-----|-------|-----|------|

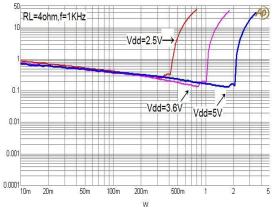

|       |                 | THD + N = 10%,<br>f = 1 kHz, RL = 4 Ω      | VDD = 5 V            |     | 3.06  |     | W    |

|       |                 |                                            | VDD = 3.6 V          |     | 1.69  |     |      |

|       |                 | 1 - 1 KHZ, KL - 4 32                       | VDD = 2.5 V          |     | 0.73  |     |      |

|       |                 | THD + N = 1%,                              | VDD = 5 V            |     | 2.53  |     |      |

|       |                 | $f = 1 \text{ kHz}, \text{ RL} = 4 \Omega$ | VDD = 3.6 V          |     | 1.36  |     | W    |

| PO    | Output power    | 1 - 1 KHZ, KL - 4 32                       | VDD = 2.5 V          |     | 0.59  |     |      |

| PU    | (per channel)   |                                            | VDD = 5 V            |     | 1.71  |     | w    |

|       |                 | THD + N = 10%,<br>f = 1 kHz, RL = 8 Ω      | VDD = 3.6 V          |     | 0.80  |     |      |

|       |                 | $I = I K \Pi Z, K L = 0.02$                | VDD = 2.5 V          |     | 0.37  |     |      |

|       |                 |                                            | VDD = 5 V            |     | 1.37  |     |      |

|       |                 | THD + N = 1%,<br>f = 1 kHz, RL = 8 Ω       | VDD = 3.6 V          |     | 0.65  | W   |      |

|       |                 | $I = I K \Pi Z, K L = 0.02$                | VDD = 2.5 V          |     | 0.30  |     |      |

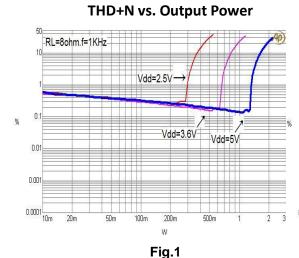

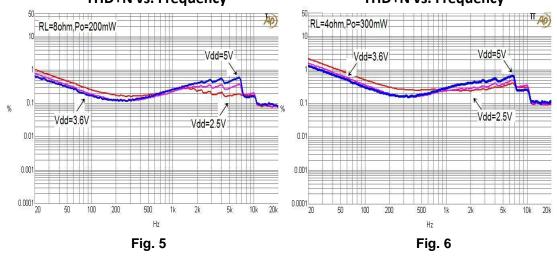

|       | Total harmonic  | VDD= 5V, PO=1W, RL=                        | =8Ω, f=1kHz          |     | 0.10% |     |      |

| THD+N | distortion plus | VDD= 3.6V, PO=0.5 W                        | RL=8 Ω, f = 1kHz     |     | 0.12% |     |      |

|       | noise           | VDD=2.5V,PO=200mW                          | , RL = 8 Ω, f = 1kHz |     | 0.15% |     |      |

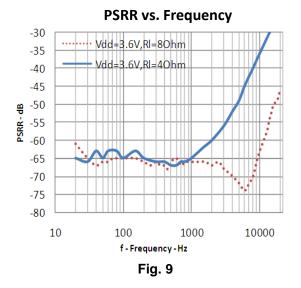

| PSRR  | Supply ripple   | VDD = 3.6 V, Inputs                        | f=217Hz,             |     | -65   |     | dB   |

| FORK  | rejection ratio | ac-grounded with Ci=2                      | uF V(ripple)=0.2Vpp  |     | -05   |     | uБ   |

| SNR   | Signal-to-noise | VDD = 5V, PO = 1W, R                       | 1 - 80               |     | 91    |     | dB   |

| SINK  | ratio           | VDD - 50, FO - 100, K                      | L = 012              |     | 91    |     | uВ   |

| Cs    | Crosstalk       | f = 1kHz                                   |                      |     | -76   |     | dB   |

|       | Start-up time   | VDD = 3.6V                                 |                      |     | 12    |     | me   |

|       | from shutdown   | VDD = 3.0V                                 |                      |     | 12    |     | ms   |

# MT6832 Ultra-low EMI, 3W Filterless Stereo Class-D Audio Amplifier

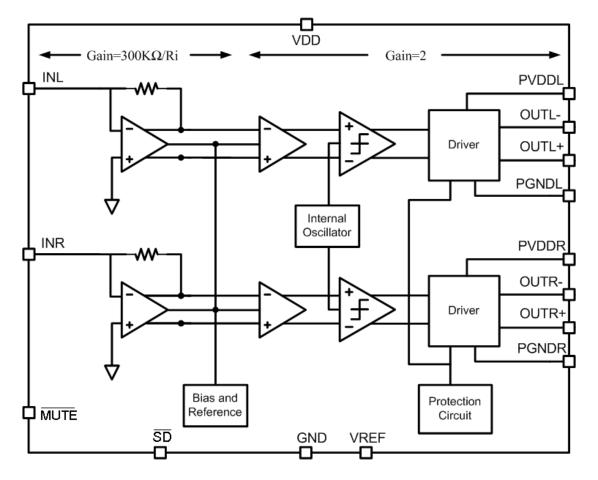

# **BLOCK DIAGRAM**

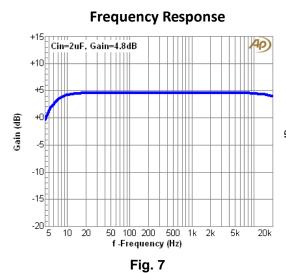

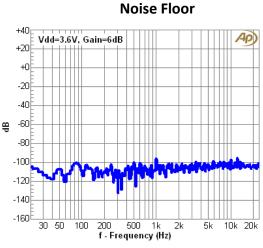

# **TYPICAL OPERATING CHARACTERISTICS (TA=25°C)**

### THD+N vs. Output Power

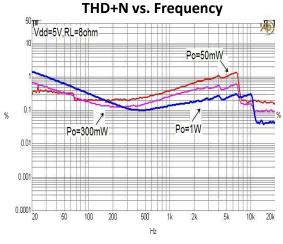

**THD+N vs. Frequency**

Po=50mW

Po=1W

21

1k

500

Hz

200

50**FT**

0.

0.01

0.001

0.0001

Vdd=5V.RL=4ohm

50 100

Po=200mW

20k

5k 10k

# MT6832 Ultra-low EMI, 3W Filterless Stereo Class-D Audio Amplifier

Fig. 8

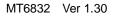

**Efficiency vs. Output Power**

## **APPLICATION INFORMATION**

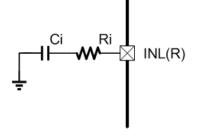

### • Inputs Setting

Only single-ended input mode is supported for MT6832. connect audio source to the INL/INR input through DC-cut capacitors (Ci) and input resistors (Ri), as Fig.14 shows.

### Fig.14. MT6832: Single-Ended Inputs

The VREF pin (Pin8) MUST connect to GND through a capacitor.

If there is one channel unused, input pin of the unused channel side, should be connected to GND through a capacitor as Fig. 15.

Fig.15. MT6832: Unused Channel Side

### • Shut down Mode

The MT6832 provides a shutdown mode to reduce supply current to the absolute minimum level during periods of non-use for battery-power conservation. The  $\overline{SD}$  input pin should be held high during normal operation when the amplifier is in use. Pulling  $\overline{SD}$  low causes the outputs to mute and the amplifier to enter a low-current state.  $\overline{SD}$  pin internally has a 300 KΩ/1MΩ resistor

pull up to VDD. When SD pin is low, the

# MT6832 Ultra-low EMI, 3W Filterless Stereo Class-D Audio Amplifier

pull-up resistance is  $1M\Omega$ . When  $\overline{SD}$  pin is high, the pull-up resistance is  $300K\Omega$ . So, this pin can be floating for normal operation.

## Mute Function

The  $\overline{MUTE}$  pin is an input for controlling the output state of the MT6832. A logic low on this pin disables the outputs, and logic high on this pin enables the outputs. This pin may be used as a quick disable or enable of the outputs without a volume fade. Since there is  $300K\Omega/1M\Omega$  pull-up resistor for this pin (When  $\overline{MUTE}$  pin is low, the pull-up

resistance is  $1M\Omega$ . When *MUTE* pin is high, the pull-up resistance is  $300K\Omega$ ), it can be floating for non-mute operation.

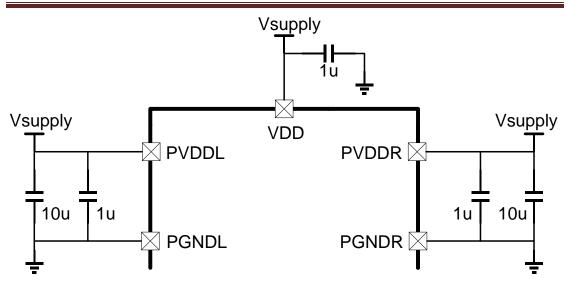

## • Power Supply Decoupling

The MT6832 is a high-performance CMOS audio amplifier that requires adequate power supply decoupling to ensure the output total harmonic distortion (THD) and PSRR are as low as possible. At this stage it is paramount that we acknowledge the need for separate power supplies and grounds. Noise currents in the output power stage need to be returned to output noise ground and nowhere else. Were these currents to circulate elsewhere, they may get into the power supply, the signal ground, etc, worse yet, they may form a loop and radiate noise. Any of these instances results in degraded amplifier performance. In the layout of the MT6832, the two channels amplifier should offer separate PVDD connections and PGND connections for each channel and

signal currents for the inputs, reference, etc need to be returned to quite power supply VDD and GND.

As Fig. 16 showing, optimum decoupling is achieved by using two capacitors of different types that target different types of noise on the power supply leads. For higher frequency transients, spikes, or digital hash on the line, a good low equivalent series resistance (ESR) ceramic capacitor, typically 1.0µF, placed as close as possible to the device VDD terminal works best. For filtering lower-frequency noise signals, a larger capacitor of 10µF (ceramic) or greater placed near the audio power amplifier is recommended, this capacitor serves as local storage capacitor for supplying current during large signal transients on the amplifier outputs.

### • Over Current Protection

The MT6832 has output short circuit protection circuitry on the outputs that prevents damage to the device during output-to-output short, output-to-GND short, and output-to-VDD short. MT6832 enters the shutdown state and the outputs are disabled when detects output short. This is a latched fault and must be reset by cycling the

### voltage on $\overline{SD}$ pin to a logic low and back

to the logic high, or by cycling the power off and then back on. This clears the short circuit flag and allows for normal operation if the short was removed. If the short was not removed, the protection circuitry actives again.

Fig.16. Power Supply Decoupling

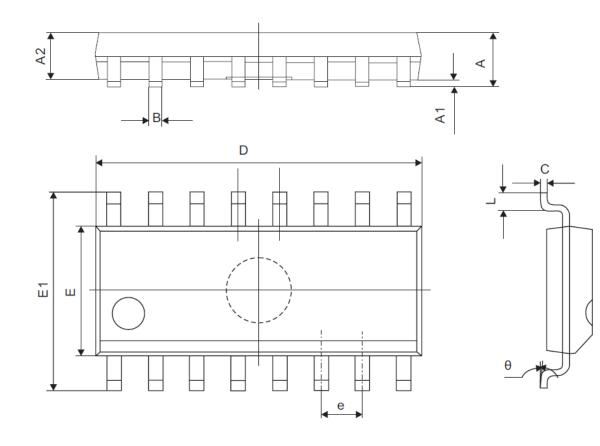

## **PACKAGE DIMENSION**

## Package: SOP16

| Symbol | Unit (mm)  |            |  |  |

|--------|------------|------------|--|--|

|        | Min        | Max        |  |  |

| Α      | 1.350      | 1.750      |  |  |

| A1     | 0.100      | 0.250      |  |  |

| A2     | 1.350      | 1.550      |  |  |

| В      | 0.330      | 0.510      |  |  |

| С      | 0.190      | 0.250      |  |  |

| D      | 9.800      | 10.000     |  |  |

| E      | 3.800      | 4.000      |  |  |

| E1     | 5.800      | 6.300      |  |  |

| е      | 1.270(TYP) |            |  |  |

| L      | 0.400      | 1.270      |  |  |

| θ      | 0°         | <b>8</b> ° |  |  |

### For detail products information and sample requests, please contact:

### Maxic Technology Corporation (Beijing Office)

1006, Crown Plaza Office Tower, No106, ZhiChun Road, Hai Dian District, Beijing, China, 100086Tel: 86-10-62662828Fax: 86-10-62662951

### Maxic Technology Coporation (Shenzhen office)

Room 1115, Qinghai Building, No.7043 North Ring Road, Futian District, Shenzhen, P.C. 518000Tel: 86-755-83021778Fax: 86-755-83021336

### Maxic Technology Corporation (Suzhou Office)

B-503, #3 Chuangye Park, 328 Xinghu Street, Indurial Park, Suzhou, 215021

Tel: 86-512-62958262

Fax: 86-512-62958262

### Maxic Technology Corporation(Indian office)

50-B, Bhatia Colony, Ballabgarh-121004,Faridabad(INDIA) E-mail: India@maxictech.com

Web: www.maxictech.com E-mail: <a href="mailto:sales@maxictech.com">sales@maxictech.com</a>, <a href="mailto:info@maxictech.com">info@maxictech.com</a>,